# **I3C Technology Training**

**Presented by Saminah Chaudhry**

Systems Engineer - Member, Group Technical Staff (MGTS)

**Transceiver Interface (Texas Instruments)**

## Agenda

- Introduction to MIPI I3C

- I3C motivation

- I3C vs I<sup>2</sup>C

- I3C protocol overview

- I3C applications in different end equipment

- TRX I3C roadmap

- Summary & key resources

# **I3C** | MIPI I3C vs JEDEC

|                                                                                                  |                                                                      |                                                                             | Legacy PC Target Compatibility)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | · •         | •   |     | 1 × × 1 |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|-----|---------|

| I3C v1.0 (2016)                                                                                  |                                                                      | I3C v1.1 (2019                                                              | I3C v1.1.1 (2021) Target can operate as IC device on IC bus and on ISC bus using HDR modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ~           | ~   | ~   | ~       |

| <ul> <li>MIPI I3C: <u>Improved inter integra</u></li> </ul>                                      | ated circuit -                                                       | <ul> <li>Advancement of MIPI I3</li> <li>New features added to a</li> </ul> | Target Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~           | ~   | ~   | ~       |

| Next gen communication interfa<br>> 12.5MHz SDR (Single dat                                      | a rate)                                                              | set of use cases and inc<br>HDR-BT (Bulk tran                               | stries: Improves on I3C v11 spec with Section 1243 30 Operation for 50of Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>x</b> 13 | ~   | ~   | ~       |

| <ul> <li>In-band Interrupt &amp; Hot-joi</li> <li>HDR-DDR (Double data rational data)</li> </ul> |                                                                      | <ul> <li>Group Addressing</li> <li>Multi-Lane for Spe</li> </ul>            | requirements In-Band Interrupt (w/MDB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ¥ 1         | × 1 | ~   | ~       |

| <ul> <li>Timing control</li> <li>HDR Ternary symbol mod</li> </ul>                               | les                                                                  | <ul> <li>Target Reset</li> <li>Device to device(s</li> </ul>                | Dynamic Address Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | × 1         | ~   |     | ~       |

|                                                                                                  |                                                                      | Device to device(s                                                          | Error Detection and Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | × 1         | × 1 | ×   | ~       |

|                                                                                                  |                                                                      |                                                                             | Secondary Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>~</b>    | ~   | × . |         |

|                                                                                                  | 120 hasta vit 0                                                      | (204.0)                                                                     | Hot-Join Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | × 1         | ~   | × . | × 1     |

| <b>/</b>                                                                                         | I3C basic v1.0<br>Feature-reduced, lower-cor                         | nplexity version                                                            | I3C basic v1.1.1 (2021) Common Command Codes (Required/Optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ~ ·         | ~   | *   | ~~      |

|                                                                                                  | of MIPI 13C v1.0 specificati<br>Functions Not Included in I          |                                                                             | Synchronized with I3C v1.1.1 Spec     Subset of I3C v1.1.1, and adds key features     Subset of I3C v1.1.1, and adds key features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | v           | ~   | ~   | ~       |

|                                                                                                  | <ul> <li>HDR-DDR (Double di</li> <li>HDR Ternary symbol</li> </ul>   |                                                                             | and capabilities: Set Static Address at Dynamic Address CCC (SETAASA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •           | ~   | ~   | ~       |

|                                                                                                  | Timing control<br>Royalty free licensing for no                      |                                                                             | transport) Mode<br>Grouped addressing Synchronous Timing Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ¥ 1         | ~   | ¥ . | 4       |

| (                                                                                                | I3C Basic Mode is used by<br>DDR5 Interface                          | JEDEC for                                                                   | Target reset     Timing control (Async mode 0 only)     Asynchronous Timing Control (Mode 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~           | ~   | ~   | ~       |

|                                                                                                  |                                                                      |                                                                             | Royalty free licensing for non-MIPI member Asynchronous Timing Control (Mode 1-3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ¥ .         | ~   | ~   | ~       |

| Features                                                                                         | JEDEC (adoption of<br>MIPI I3C basic 1.0)                            | MIPI 13C<br>(v1.0)                                                          | Evolution of MIPI I3C interface specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | v           | ~   | ~   | ~       |

| 12.5MHz SDR                                                                                      | Yes                                                                  | Yes                                                                         | 12C stendard status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |     |     |         |

| High Data Rate modes                                                                             | No                                                                   | Yes                                                                         | I3C standard status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ×           | × 1 | × 1 | ×       |

| Dynamic Address Assignment                                                                       | No                                                                   | Yes                                                                         | I3C v1.1.1     HDR-BT (Multi-Lane Bulk Transport)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | v 📘         | ~   | ~   | ~       |

| In-Band-Interrupt                                                                                | Yes                                                                  | Yes                                                                         | I3C spec is mature and not sensitive to spec changes. No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |     | -   |         |

| Hot-Join                                                                                         | No                                                                   | Yes                                                                         | revisions of I3C v1.1.1 expected, no new approved features. Grouped Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | × 📘         | × I | × 1 | × .     |

| Target Reset                                                                                     | No                                                                   | Yes (MIPI I3C v1.1)                                                         | ISC Basic v1.1.1      Events and with ISC v1.1.1 Device to Even and the ISC v1.1.1 Device to Device t |             | ~   | 6   | ~       |

| Timing Control                                                                                   | No                                                                   | Yes                                                                         | • Synchronized with ISC VI.1.1, subset of WiFT ISC VI.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | · •         | · I |     | · ·     |

| Common Command Controls (CCC)                                                                    | Small subset of MIPI I3C<br>(8 CCCs)                                 | >50 CCCs                                                                    | specification, royalty free licensing for non-MIPI members.     Multi-Lane for Speed     (Dual/Quad for SDR and HDR-DDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>~</b>    | ~   | ×   | ×.      |

| Error Detection/Recovery<br>Clock LOW timeout                                                    | Conformance Test Suite (CTS) for I3C v1.1.1 and I3C Basic     v1.1.1 | ~                                                                           | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ~           | ~   |     |         |

🔱 Texas Instruments

**Comparison of Features**

Feature

13C v1.0 I3C Basic I3C I3C Basic v1.0 v1.1.1 v1.1.1

# I3C vs I<sup>2</sup>C

| Feature                        | I3C                                                               | I <sup>2</sup> C              |  |  |

|--------------------------------|-------------------------------------------------------------------|-------------------------------|--|--|

| SCL max frequency              | 12.5 MHz                                                          | 1 MHz (FM+ mode)              |  |  |

| IO topology                    | SCL: Push pull; SDA: Open drain and push pull                     | SCL & SDA: Open drain only    |  |  |

| Capacitive load per bus line   | 50 pF                                                             | 400 pF for FM; 550 pF for FM+ |  |  |

| Bus pull-up resistor           | Integrated in the host controller                                 | External pull up              |  |  |

| Interrupt                      | In band                                                           | Dedicated pin                 |  |  |

| Compatibility                  | Supports I <sup>2</sup> C target devices with 50 ns glitch filter | No support                    |  |  |

| Dynamic addressing             | Yes                                                               | No                            |  |  |

| 9 <sup>th</sup> bit function   | ACK or NACK (address), Parity (write) and Bus control (read)      | ACK or NACK                   |  |  |

| Bus functions                  | Common code commands (CCC)                                        | Special address               |  |  |

| Device feature support         | 3 mandatory registers: BCR, DCR, LVR                              | No                            |  |  |

| Bus compliance                 | Yes, established as interoperability rules                        | No                            |  |  |

| Target reset                   | Unique pattern based                                              | Hard-reset line               |  |  |

| Target device clock stretching | Not allowed on I3C                                                | Yes                           |  |  |

| Extended address (10 bit)      | Not used on I3C                                                   | Optional                      |  |  |

| 20 mA open drain driver        | Not used on I3C                                                   | Supported in FM+ mode         |  |  |

# **I3C** | Motivation

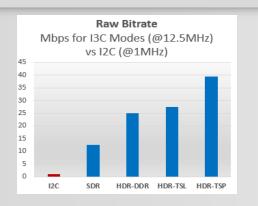

### Fast efficient communication channel

- Multidrop SDA/SCL 2-wire interface

- 12.5 MHz max clock rate

- 1.2V-3.3V voltage supported

- Physical layer CMOS I/O compatible

- Dynamic switch between pullup/push pull/Hi-Z

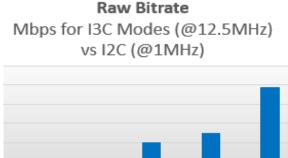

- SDR (Single Data Rate) 12.5 Mbps

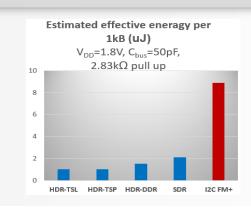

- HDR (High Data Rate) modes for higher throughput (HDR-DDR, HDR-TSL, HDR-TSP, HDR-BT)

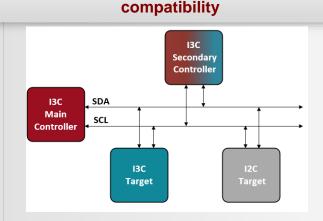

System management & backward

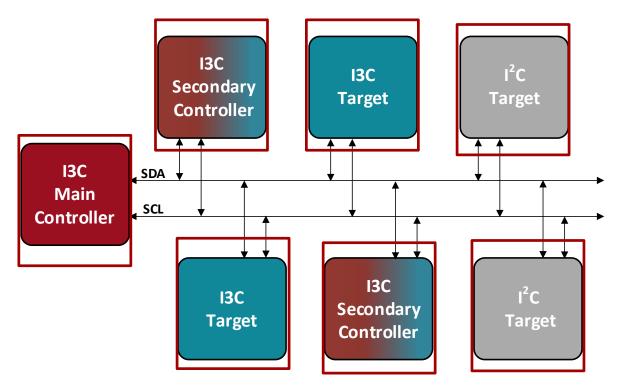

- Device Roles: I3C primary & secondary Controllers

- Dynamic address assignment (including group addressing)

- Standardized commands for bus management, configuration and control

- Backwards compatible allowing mixed bus operation

### Advanced functions

- Broadcast & direct messages

- Error detection & recovery, parity, CRC

- Target reset

- In-band interrupt (IBI)

- Hot-join

- Timing control

- Power efficiency

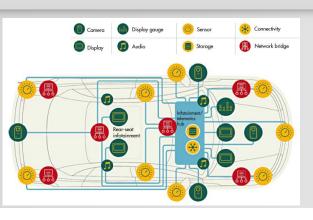

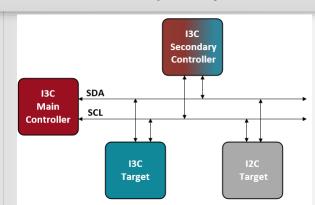

# **I3C** | Controller and target device roles

I3C bus with I2C devices and I3C devices

# **I3C protocol**

Single Data Rate (SDR) Mode

# **I3C** | Bus communication - (SDR) mode

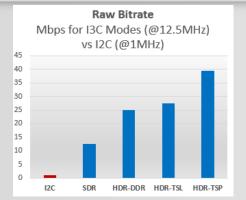

Communication protocols for all defined I3C Modes include:

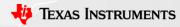

- Single data rate (SDR) mode 12.5 Mbit/s

- High data rate (HDR) modes

- HDR-DDR (Dual data rate) 25 Mbit/s

- HDR-TSL (Ternary symbol legacy) 27.5 Mbit/s

- HDR-TSP (Ternary symbol pure) 39.5 Mbit/s

- HDR-BT (Bulk transport) data rate up to 100 Mbps

- ML data transfer available for any I3C Mode (e.g., SDR, HDR-DDR, HDR-TSP, or HDR-BT)

### Single Data Rate (SDR)

- Default Mode of the I3C Bus

- SCL wire operates as Clock signal driven by Controller, while data is transferred using SDA wire

- Used to enter other modes, sub-modes, and states for built-in features

45 40

35

30

25

20 15

10

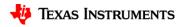

# **I3C** | Frame structure vs I<sup>2</sup>C

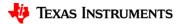

# **I3C | SDR address arbitration**

- Address Header following a START is an <u>arbitrable address header</u>

- I3C Uses Clock Speed to Prevent Legacy I<sup>2</sup>C Devices from Seeing I3C Traffic

- SCL high-period is <45ns, well below 50ns glitch filter required by I<sup>2</sup>C, enabling up to ~ 4MHz

- After ACK, the controller changes SDA to push-pull mode and increases its clock to 12.5MHz

- I3C maximum bus frequency: 12.5MHz (80 ns) clock period

- SDR Mode is backwards compatible with legacy I<sup>2</sup>C devices; to coexist in the same bus, spike suppression filter of 50ns avoids any interference to the bus when communicating with I3C device

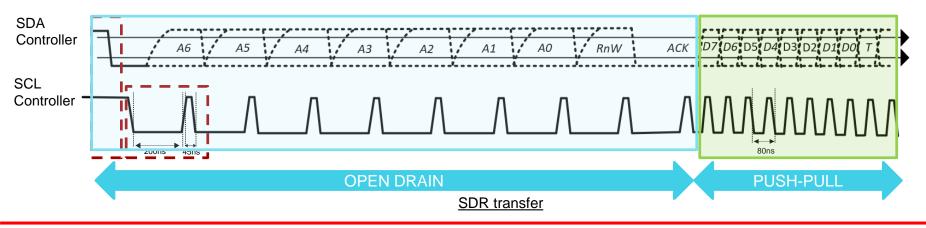

# **I3C** | Bus communication - (SDR) mode

- I3C <u>START</u> and <u>STOP</u>: Identical to the I<sup>2</sup>C START and STOP in their signaling, but they may vary from I<sup>2</sup>C in their timing

- I3C <u>Address Header</u>: Identical to the I<sup>2</sup>C address header in bit form and in signaling, but it may vary from I<sup>2</sup>C in its timing.

- Data 9-bit Words: Same bit count as I<sup>2</sup>C, but differ in the ninth bit

TI Information - Selective Disclosure

# **I3C | SDR data word – 9th bit**

In I3C SDR, the data words match I<sup>2</sup>C only in the sense that they are both 9 bits long.

### Ninth Bit of SDR Controller written data as parity:

- In I3C the ninth data bit written by the controller is the **parity** of the preceding eight data bits.

- In SDR terms, the ninth bit of write data is referred to as the T-Bit (for 'Transition')

- Parity can help in detecting noise-caused errors on the line

|                  | 1 bit            | 8 bits   | 1 bit    | 8 bits      | 1 bit          |           | 1 bit               |

|------------------|------------------|----------|----------|-------------|----------------|-----------|---------------------|

| <b>MIPI 130</b>  | S/S <sub>R</sub> | Addr + W | ACK/NACK | 1 Byte data | T bit = Parity | More data | S <sub>R</sub> or P |

| l <sup>2</sup> C |                  |          |          |             | ACK/NACK       |           |                     |

### Ninth Bit of SDR target returned (read) data as end-of-data:

- In I3C 9th bit allows the <u>target to end a read</u>, and allows the <u>controller to abort a read</u>.

- In SDR terms, the ninth bit of read data is referred to as the T-Bit (for 'Transition')

- T-bit allows negotiation between host and device for read data

|                  | 1 bit            | 8 bits   | 1 bit        | 8 bits      | 1 bit          | 1 bit          | 8 bits   | 1 bit | 8 bits      | 1 bit                                  |           | 1 bit                                            |

|------------------|------------------|----------|--------------|-------------|----------------|----------------|----------|-------|-------------|----------------------------------------|-----------|--------------------------------------------------|

| MIPI I3C         | S/S <sub>R</sub> | Addr + W | ACK/<br>NACK | 1 Byte data | T bit = Parity | S <sub>R</sub> | Addr + R |       | i Dyie dala |                                        | More data | S <sub>R</sub> or P<br>(Controller<br>ends read) |

| l <sup>2</sup> C |                  |          |              |             | ACK/<br>NACK   |                |          |       |             | ACK/NACK<br>Target can't<br>abort read |           | (Controller<br>ends read)                        |

# **I3C** | Characteristic registers

I3C characteristics registers describe and define an I3C compatible device's **capabilities and functions** on the I3C bus, as the device services a given system.

# Bus characteristics register (BCR)

Describes I3C compliant device's role and capabilities for use in dynamic address assignment and common command codes

• For example, IBI request capable, max data speed limitation)

### Device characteristics register (DCR)

Describes the I3C compliant device type (For example, accelerometer, gyroscope, etc.)

- 255 available codes for describing the type of sensor, or device.

- Default value is 8'b0: generic device

# Legacy virtual register (LVR)

Describes I<sup>2</sup>C legacy device's significant features

allowed I<sup>2</sup>C modes and maximum SCL clock frequency of I<sup>2</sup>C device connected on an I3C bus)

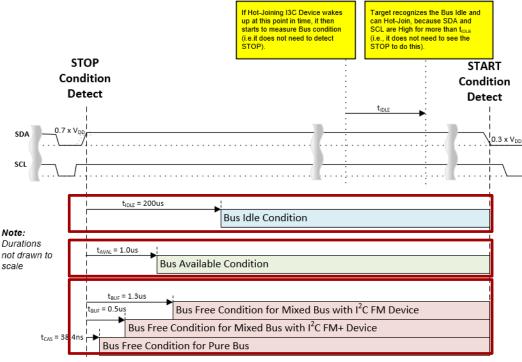

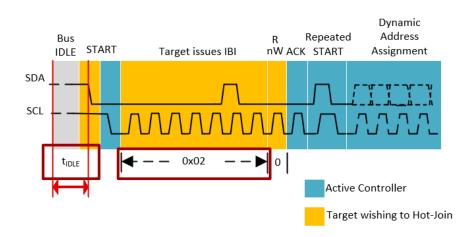

# **I3C** | Bus condition timing definitions

Bus conditions are defined from STOP on the bus:

- t<sub>CAS</sub> is referred as bus free time and period occurring after a STOP and before a START

- For <u>Pure bus</u>: A duration of at least t<sub>CAS</sub>

- For <u>Mixed bus (i.e., at least one legacy  $I^2C$  device is present on the I3C Bus): A duration of atleast  $t_{BUF}$ </u>

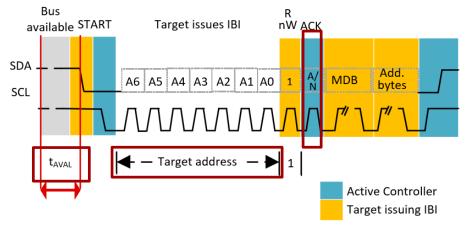

- t<sub>AVAL</sub> is referred as bus available time and is the minimum time the target device must wait before asserting in-band-interrupt

- t<sub>IDLE</sub> is referred as bus Idle time and is the minimum time a non-participating device must wait before requesting hot-join

- A requesting device does not need to monitor Stop if it sees bus idle for t<sub>IDLE</sub> duration.

Bus condition timing

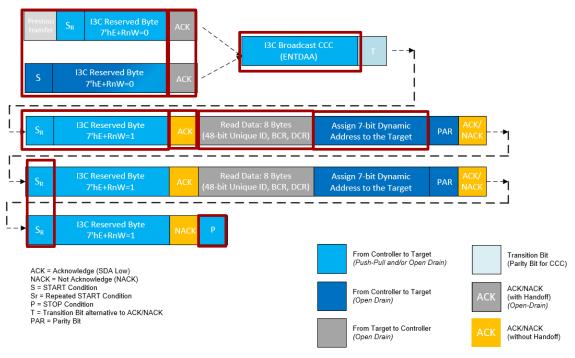

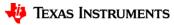

# **I3C** | Dynamic address assignment (DAA)

- Regular exchanges on the I3C bus require a dynamic 7-bit address

- In order to support dynamic address assignment procedure, each MIPI I3C device to be connected to I3C bus shall be uniquely identifiable in <u>one of two ways</u> before starting the procedure:

### **1. Device has static address**

- SETDASA: (<u>Direct CCC</u>) The primary controller assigns dynamic addresses to <u>ANY</u> I3C devices with a known static address using SETDASA

- SETAASA: (Broadcast CCC) The primary controller assigns <u>ALL</u> I3C devices their known I<sup>2</sup>C static address using SETAASA

### 2. Device supports ENTDAA

Device that supports broadcast command code ENTDAA shall have its own <u>48-bit provisional ID</u> (PID)

- <u>15 bits for MIPI manufacturer ID</u>

- <u>1 bit indication if the below values are random</u>

or not

- <u>32 bits</u> for part ID, instance ID and some bits reserved for vendor definition

- PID, BCR and DCR will be advertised during the DAA procedure

# **I3C** | Dynamic address assignment (DAA)

Dynamic address assignment transaction

# **I3C** In band interrupt (IBI)

- Device driven in-band interrupts handled through I3C BUS

- The device can raise an interrupt in the following condition:

- Target device can issue START request when in "bus available" state and waits for the controller to acknowledge the interrupt by pulling SCL low to end the start condition

- Controller provides interface clock for target to drive it's controller-assigned address onto the bus

- Lowest assigned address wins arbitration in opendrain configuration; controller ACKs or NACKs the interrupt

- Some devices may also provide a mandatory byte that the controller must read

- Fast and efficient asynchronous data acquisition, and event processing

- Avoids extra dedicated wires or inefficient polling mechanism

# I3C | Hot-join (HJ)

Allows I3C targets to join the bus after it has already been configured

- Target must wait for a bus idle condition before sending the hot-join request

- Target sends a special in-band-interrupt (IBI) request to trigger the hot-join procedure.

- Joining target issues reserved target address with predefined high-priority

- Controller initiate a new dynamic address assignment (DAA) procedure.

- Unlike typical IBI, hot-join does not have data payload or mandatory data byte

- Improved power management, energy savings

- Selective powering of sub-units

- Wake-up only when needed

### Ideal for I3C Devices:

- Mounted on the same board, but de-powered until needed

- Mounted on module/board that is physically inserted after I3C bus has already been configured

# **I3C** | Timing control

I3C includes optional timing control and timestamping of events generated by I3C devices resident on the I3C Bus

### Synchronous time control

- Controller periodically emits a synchronization pulse

- Targets collect the data at synchronized times, so that the controller can read several targets' data in a single system awake period

Avoids drift of individual targets' clocks

Ensures that samples occur close together in time

### Asynchronous timing control

Target device <u>timestamps</u> events occurring within that target at a particular frequency, and then notifies the controller about it by generating an In-band interrupt (IBI)

- Four Async modes

- Basic Async mode 0

- Enhanced Async mode 1, 2 & 3

- Controller always has the time information at which target data acquisition occurred

# **I3C** | Common command codes (CCC)

I3C standardized command set for interaction between host and device(s).

- Used for standard operations like enabling/disabling events, managing I3C-specific features, and other Bus operations

- In I<sup>2</sup>C the similar function was achieved using special address

- Built-in Commands (>40) in separate "space" to avoid collision with normal controller to target messages

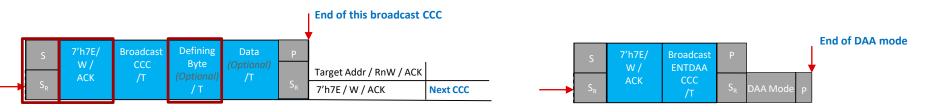

### Type of command frames

Broadcast CCC → Host to all I3C devices

• All Broadcast CCCs are write CCCs (Command codes 0x00 to 0x7F)

Direct CCC → Host to specific devices

• Three types of Direct CCCs: Read, write, and read/write (command codes from 0x80 to 0xFE)

### **CCC** Implementation

<u>Mandatory</u>: Every I3C device must support it. E.g., ENEC for enabling events for interrupt. <u>Conditional</u>: If certain features are required, then these must be implemented. E.g. SETNEWDA for dynamic address reassignment and implemented only if ENTDAA is supported. <u>Optional</u>: Implementation specific. E.g. SETDASA for dynamic address assignment to a device with a

known static address.

# **I3C** | Common command codes (CCC) format

CCC broadcast general frame format

Example: "ENTDAA" format

CCC direct general frame format

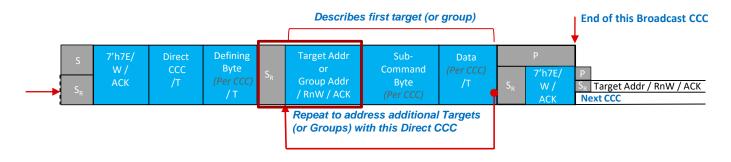

# **I3C | Target reset**

- Allows the controller to reset one or more selected targets

- Target reset pattern is used to trigger the default or configured reset action

- RSTACT CCC specifies how the targets should react to a "reset pattern":

- Discard

- Reset the bus controller

- Reset the entire chip

- Target Reset Pattern begins with 14 SDA transitions while SCL is kept Low, and ends with a repeated START followed by a STOP which triggers the actual reset action.

- Useful in avoiding deadlocks on the bus due to an unresponsive device

- Avoids extra dedicated wires for reset

# **I3C** | Error detection & recovery

- The MIPI I3C bus specification details error detection and error recovery methods for an SDR target, the I3C controller and HDR mode(s)

- A set of 6 mandated methods and 2 optional methods are specified for MIPI I3C target devices, and a separate set of required methods is specified for MIPI I3C controller devices.

- Help avoid fatal conditions when errors occur

| Error Type     | Description                              |  |  |  |  |  |  |

|----------------|------------------------------------------|--|--|--|--|--|--|

| CE0            | Transaction after sending CCC            |  |  |  |  |  |  |

| CE1 (optional) | Monitoring error                         |  |  |  |  |  |  |

| CE2            | No response to broadcast address (7'h7E) |  |  |  |  |  |  |

| CE3            | Failed controller handoff                |  |  |  |  |  |  |

| Error Type     | Description                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------|

| TE0            | Invalid broadcast address/W (7'h7E/W)<br>or dynamic address/RnW after dynamic<br>address assignment |

| TE1            | CCC code                                                                                            |

| TE2            | Write data                                                                                          |

| TE3            | Assigned address during dynamic address arbitration                                                 |

| TE4            | 7'h7E/R missing after Sr during dynamic address arbitration                                         |

| TE5            | Transaction after detecting CCC                                                                     |

| TE6 (optional) | Monitoring error                                                                                    |

| DBR (optional) | Dead bus recovery                                                                                   |

SDR target error types

SDR controller error types

TI Information - Selective Disclosure

# **I3C Protocol**

High data rate (HDR) modes & multi-lane (ML) data transfer

# **I3C** | High data rate (HDR) modes

TI Information - Selective Disclosure

Texas Instruments

# I3C | Multi Iane (ML) mode

- ML mode employs any available additional physical wires to transfer the data payload faster.

- In ML the normal I3C SDA line is referred to as SDA[0], and the additional wires are called SDA[1], SDA[2], and SDA[3].

- During ML data transfers, activity on the additional data wire(s) (i.e., SDA[1], SDA[2], and SDA[3]) would not be visible to any non-ML Devices that might be resident on that Bus

- Reduced energy consumption and increased flexibility in adding features

- An application with a camera module using quad Lanes, IMU using Dual lanes

| No. of                   | Lane                                            |                        | n Multi- Data Total<br>Lane? Wires Wires | Data | Total  | Wires Supported |        |              |              |              |

|--------------------------|-------------------------------------------------|------------------------|------------------------------------------|------|--------|-----------------|--------|--------------|--------------|--------------|

| Additional<br>Data Wires | Configuration                                   | Description            |                                          | SCL  | SDA[0] | SDA[1]          | SDA[2] | SDA[3]       |              |              |

| 0                        | SINGLE                                          | Ordinary<br>2-Wire I3C | Ν                                        | 1    | 2      | $\checkmark$    | ~      | -            | -            | -            |

| 1                        | DUAL                                            | Multi-Lane             | Y                                        | 2    | 3      | $\checkmark$    | ✓      | $\checkmark$ | -            | -            |

| 3                        | QUAD                                            | Data<br>Transfer       | Y                                        | 4    | 5      | $\checkmark$    | ~      | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 2,<br>4 through 7        | Reserved for future definition by MIPI Alliance |                        |                                          |      |        |                 |        |              |              |              |

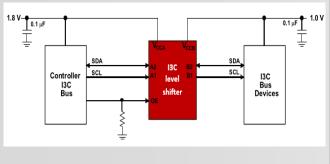

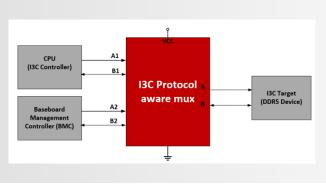

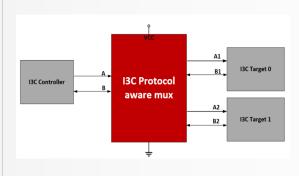

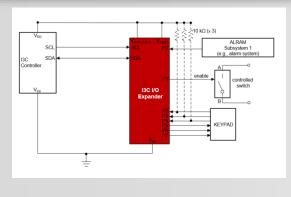

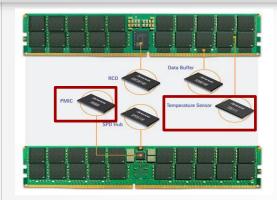

| ML configurations        |                                                 |                        |                                          |      |        |                 |        | 26           |              |              |